# Numonyx™ StrataFlash<sup>®</sup> Cellular Memory ∞(M18)

#### **Datasheet**

#### **Product Features**

- High-Performance Read, Program and Erase

- 96 ns initial read access

- 108 MHz with zero wait-state synchronous burst reads: 7 ns clock-to-data output

- 133 MHz with zero wait-state synchronous burst reads: 5.5 ns clock-to-data output

- 8-, 16-, and continuous-word synchronous-burst Reads

- Programmable WAIT configuration

- Customer-configurable output driver impedance

- Buffered Programming:

2.0 μs/Word (typ), 512-Mbit 65 nm;

Block Erase: 0.9 s per block (typ)

- 20 μs (typ) program/erase suspend

- Architecture

- 16-bit wide data bus

- Multi-Level Cell Technology

- Symmetrically-Blocked Array Architecture

- 256-Kbyte Erase Blocks

- 1-Gbit device: Eight 128-Mbit partitions

- 512-Mbit device: Eight 64-Mbit partitions

- 256-Mbit device: Eight 32-Mbit partitions.

- 128-Mbit device: Eight 16-Mbit partitions.

- Read-While-Program and Read-While-Erase

- Status Register for partition/device status

- Blank Check feature

- Quality and Reliability

- Expanded temperature: -30 °C to +85 °C

- Minimum 100,000 erase cycles per block

- ETOX™ X Process Technology (65 nm)

- ETOX™ IX Process Technology (90 nm)

#### Power

- Core voltage: 1.7 V 2.0 V

- I/O voltage: 1.7 V 2.0 V

- Standby current: 60 μA (typ) for 512-Mbit,65 nm

- Deep Power-Down mode: 2 μA (typ)

- Automatic Power Savings mode

- 16-word synchronous-burst read current:

23 mA (typ) @ 108 MHz; 24 mA (typ) @

133 MHz

#### Software

- Numonyx™ Flash Data Integrator

(Numonyx™ FDI) optimized

- Basic Command Set and Extended Command Set compatible

- Common Flash Interface

#### Security

- OTP Registers:

- 64 unique pre-programmed bits 2112 user-programmable bits

- Absolute write protection with  $V_{pp} = GND$

- Power-transition erase/program lockout

- Individual zero-latency block locking

- Individual block lock-down

- Density and Packaging

- Density: 128-, 256-, and 512-Mbit, and 1-Gbit

- Address-data multiplexed and nonmultiplexed interfaces

- x16D (105-ball) Flash SCSP

- x16C (107-ball) Flash SCSP

- 0.8 mm pitch lead-free solder-ball

Order Number: 309823-11 April 2008 ww.DataSheet4U.com

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH NUMONYX™ PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN NUMONYX'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NUMONYX ASSUMES NO LIABILITY WHATSOEVER, AND NUMONYX DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF NUMONYX PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Numonyx products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Numonyx B.V. may make changes to specifications and product descriptions at any time, without notice

Numonyx B.V. may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Numonyx reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Numonyx sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Numonyx literature may be obtained by visiting the Numonyx website at <a href="http://www.numonyx.com">http://www.numonyx.com</a>.

Numonyx, the Numonyx logo, and StrataFlash are trademarks or registered trademarks of Numonyx B.V. or its subsidiaries in other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2008, Numonyx B.V., All Rights Reserved.

Datasheet April 2008

2 Order Number: 309823-11

# Contents

| 4.0 |       |                                                 | _  |  |  |  |  |  |  |  |

|-----|-------|-------------------------------------------------|----|--|--|--|--|--|--|--|

| 1.0 | Intro | oduction                                        |    |  |  |  |  |  |  |  |

|     | 1.1   | Document Purpose                                | 8  |  |  |  |  |  |  |  |

|     | 1.2   | Nomenclature                                    | 8  |  |  |  |  |  |  |  |

|     | 1.3   | Acronyms                                        | 8  |  |  |  |  |  |  |  |

|     | 1.4   | Conventions                                     | 9  |  |  |  |  |  |  |  |

| 2.0 | Eupo  | tional Description                              | 10 |  |  |  |  |  |  |  |

| 2.0 | 2.1   | •                                               |    |  |  |  |  |  |  |  |

|     | 2.1   | Product Overview                                |    |  |  |  |  |  |  |  |

|     |       | Configuration and Memory Map                    |    |  |  |  |  |  |  |  |

|     | 2.3   | Device ID                                       | 12 |  |  |  |  |  |  |  |

| 3.0 | Pack  | age Information                                 | 13 |  |  |  |  |  |  |  |

| 4.0 | Ballo | outs and Signal Descriptions                    | 23 |  |  |  |  |  |  |  |

|     | 4.1   | Ballouts, x16D                                  |    |  |  |  |  |  |  |  |

|     |       | 4.1.1 x16D (105-Ball) Ballout, Non-Mux          |    |  |  |  |  |  |  |  |

|     |       | 4.1.2 x16D (105-Ball) Ballout, AD-Mux           |    |  |  |  |  |  |  |  |

|     |       | 4.1.3 x16D Mux (105-Ball) Ballout, AA/D Mux     |    |  |  |  |  |  |  |  |

|     | 4.2   | Signal Descriptions, x16D                       |    |  |  |  |  |  |  |  |

|     | 4.3   | Ballouts, x16C                                  |    |  |  |  |  |  |  |  |

|     | 4.5   | 4.3.1 x16C (107-Ball) Ballout, Non-Mux          |    |  |  |  |  |  |  |  |

|     |       | 4.3.2 x16C (107-Ball) Ballout, NO1-Mux          |    |  |  |  |  |  |  |  |

|     |       | 4.3.3 x16C (107-Ball) Ballout, AA/D-Mux         |    |  |  |  |  |  |  |  |

|     | 4.4   | Signal Descriptions x16C                        |    |  |  |  |  |  |  |  |

|     | 4.4   | Ballouts, x16 Split Bus                         |    |  |  |  |  |  |  |  |

|     | 4.5   | 4.5.1 x16 Split Bus (165-Ball) Ballout, Non-Mux |    |  |  |  |  |  |  |  |

|     | 1 4   | Signal Descriptions, x16 Split Bus              |    |  |  |  |  |  |  |  |

|     | 4.6   |                                                 |    |  |  |  |  |  |  |  |

| 5.0 | Maxi  | Maximum Ratings and Operating Conditions        |    |  |  |  |  |  |  |  |

|     | 5.1   | Absolute Maximum Ratings                        | 42 |  |  |  |  |  |  |  |

|     | 5.2   | Operating Conditions                            | 42 |  |  |  |  |  |  |  |

| 6.0 | Flect | rical Characteristics                           | 43 |  |  |  |  |  |  |  |

| 0.0 | 6.1   | Initialization                                  |    |  |  |  |  |  |  |  |

|     | 0.1   | 6.1.1 Power-Up/Down Characteristics             |    |  |  |  |  |  |  |  |

|     |       | 6.1.2 Reset Characteristics                     |    |  |  |  |  |  |  |  |

|     |       | 6.1.3 Power Supply Decoupling                   |    |  |  |  |  |  |  |  |

|     | 6.2   | 113 1 0                                         |    |  |  |  |  |  |  |  |

|     | 6.3   | DC Current Specifications                       |    |  |  |  |  |  |  |  |

|     |       | DC Voltage Specifications                       |    |  |  |  |  |  |  |  |

|     | 6.4   | Capacitance                                     |    |  |  |  |  |  |  |  |

| 7.0 | NOR   | Flash AC Characteristics                        | 48 |  |  |  |  |  |  |  |

|     | 7.1   | AC Test Conditions                              | 48 |  |  |  |  |  |  |  |

|     | 7.2   | Read Specifications                             | 49 |  |  |  |  |  |  |  |

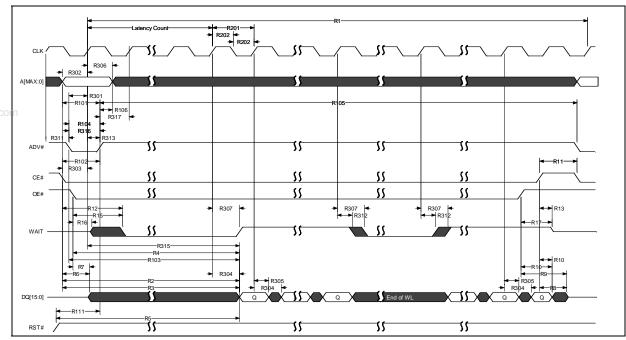

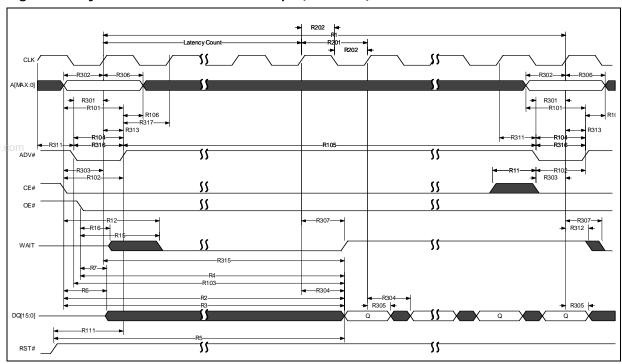

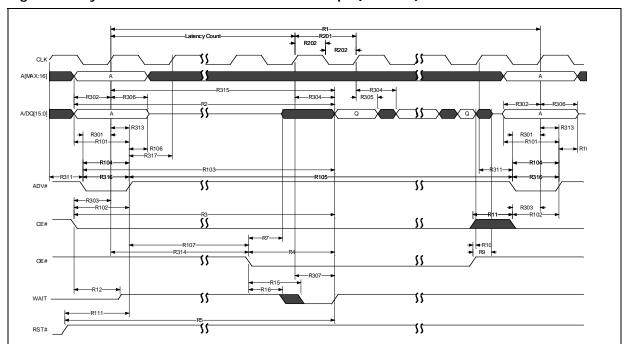

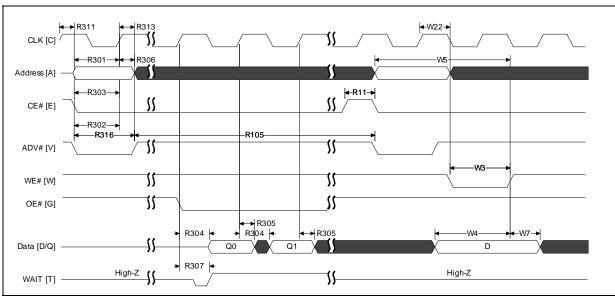

|     |       | 7.2.1 Read Timing Waveforms                     | 52 |  |  |  |  |  |  |  |

|     |       | 7.2.2 Timings: Non-Mux Device, Async Read       | 53 |  |  |  |  |  |  |  |

|     |       | 7.2.3 Timings: Non-Mux Device, Sync Read        | 54 |  |  |  |  |  |  |  |

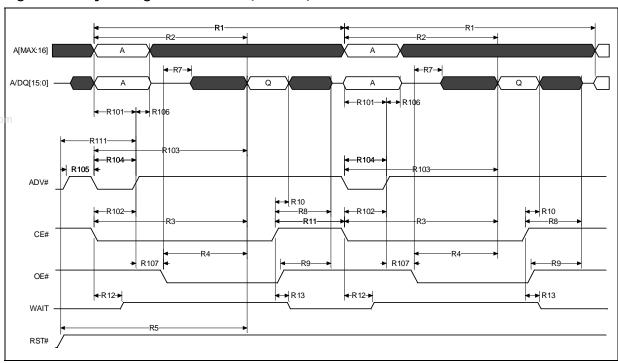

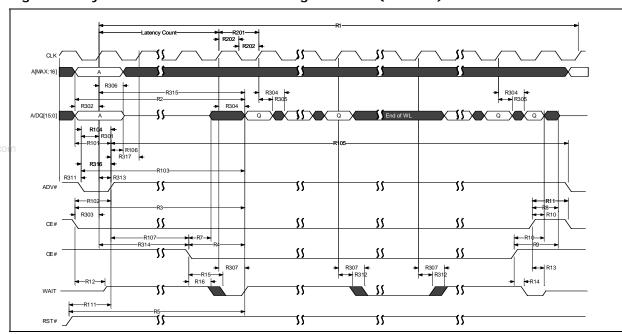

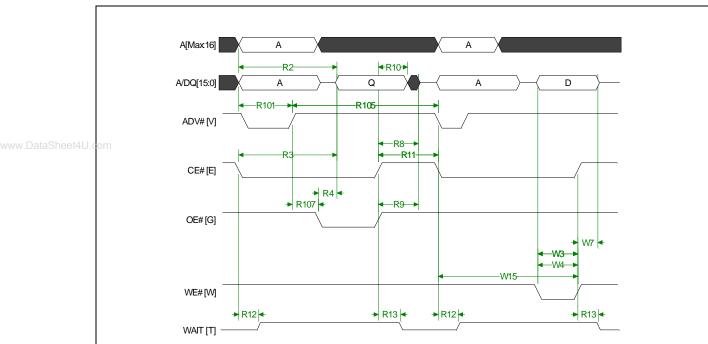

|     |       | 7.2.4 Timings: AD-Mux Device, Async Read        |    |  |  |  |  |  |  |  |

|     |       | 7.2.5 Timings: AD-Mux Device, Sync Read         |    |  |  |  |  |  |  |  |

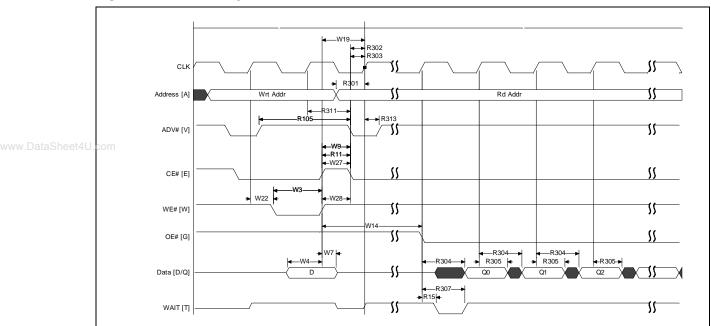

|     | 7.3   | Write Specifications                            |    |  |  |  |  |  |  |  |

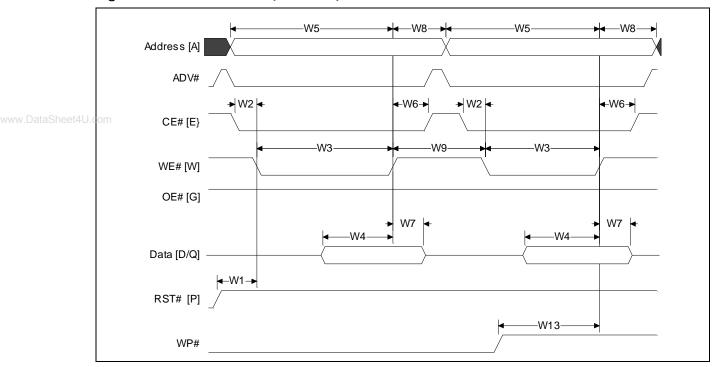

|     |       | 7.3.1 Write Timing Waveforms                    |    |  |  |  |  |  |  |  |

|     |       | 7.3.2 Timings: Non Mux Device                   |    |  |  |  |  |  |  |  |

|     |       | 7.3.3 Timings: AD-Mux Device                    |    |  |  |  |  |  |  |  |

|     | 7.4   | Program and Frase Characteristics               | 68 |  |  |  |  |  |  |  |

|        | 7.5        | Reset Specifications                                        |     |

|--------|------------|-------------------------------------------------------------|-----|

|        | 7.6        | Deep Power Down Specifications                              | 69  |

| 8.0    | NOR        | Flash Bus Interface                                         | 71  |

|        | 8.1        | Bus Reads                                                   |     |

|        | 0.1        | 8.1.1 Asynchronous single-word reads                        |     |

|        |            | 8.1.2 Asynchronous Page Mode (Non-multiplexed devices only) |     |

|        |            | 8.1.3 Synchronous Burst Mode                                |     |

|        | 8.2        | Bus Writes                                                  |     |

|        | 8.3        | Reset                                                       |     |

|        | o.s<br>8.4 | Deep Power-Down                                             |     |

|        |            | ·                                                           |     |

|        | 8.5        | Standby                                                     |     |

| 4U.com | 8.6        | Output Disable                                              |     |

|        | 8.7        | Bus Cycle Interleaving                                      |     |

|        | 0.0        | 8.7.1 Read Operation During Program Buffer fill             |     |

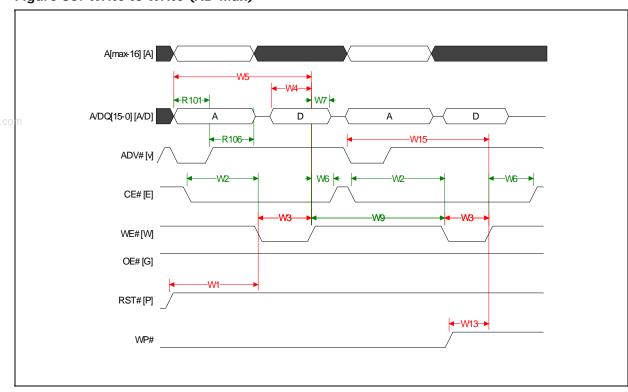

|        | 8.8        | Read-to-Write and Write-to-Read Bus Transitions             |     |

|        |            | 8.8.1 Write to Asynchronous read transition                 |     |

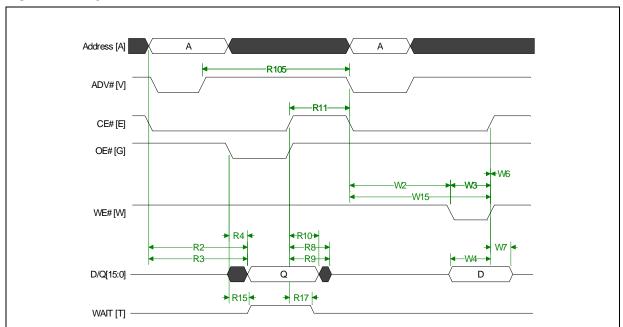

|        |            | 8.8.2 Write to synchronous read transition                  | /5  |

|        |            | 8.8.3 Asynchronous/Synchronous read to write transition     |     |

|        |            | 8.8.4 Bus write with active clock                           | 75  |

| 9.0    | NOR        | Flash Operations                                            | 76  |

|        | 9.1        | Status Register                                             |     |

|        |            | 9.1.1 Clearing the Status Register                          | 77  |

|        | 9.2        | Read Configuration Register                                 |     |

|        |            | 9.2.1 Latency Count                                         |     |

|        | 9.3        | Enhanced Configuration Register                             |     |

|        | 7.0        | 9.3.1 Output Driver Control                                 |     |

|        |            | 9.3.2 Programming the ECR                                   |     |

|        | 9.4        | Read Operations                                             |     |

|        | , , ,      | 9.4.1 Read Array                                            |     |

|        |            | 9.4.2 Read Status Register                                  |     |

|        |            | 9.4.3 Read Device Information                               |     |

|        |            | 9.4.4 CFI Query                                             |     |

|        | 9.5        | Programming Modes                                           |     |

|        | 7.5        | 9.5.1 Control Mode                                          |     |

|        |            | 9.5.2 Object Mode                                           |     |

|        | 9.6        | Programming Operations                                      |     |

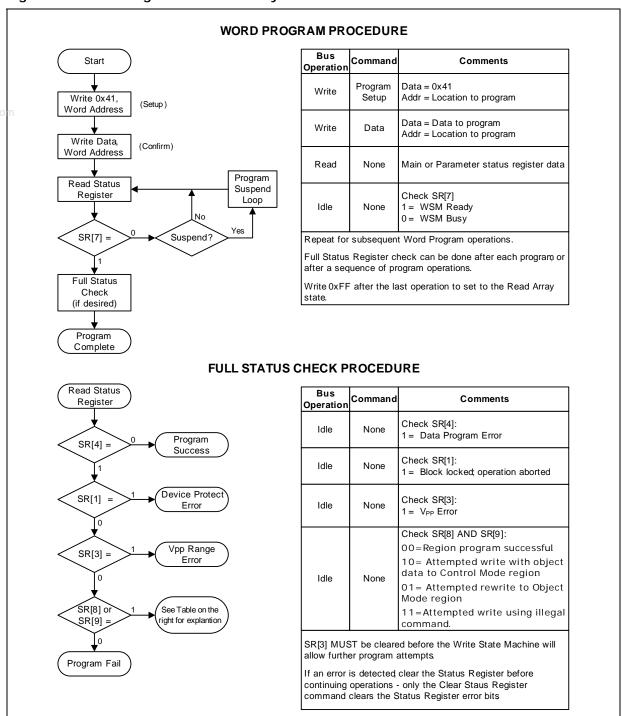

|        | 7.0        | 9.6.1 Single-Word Programming                               |     |

|        |            | 9.6.2 Buffered Programming                                  |     |

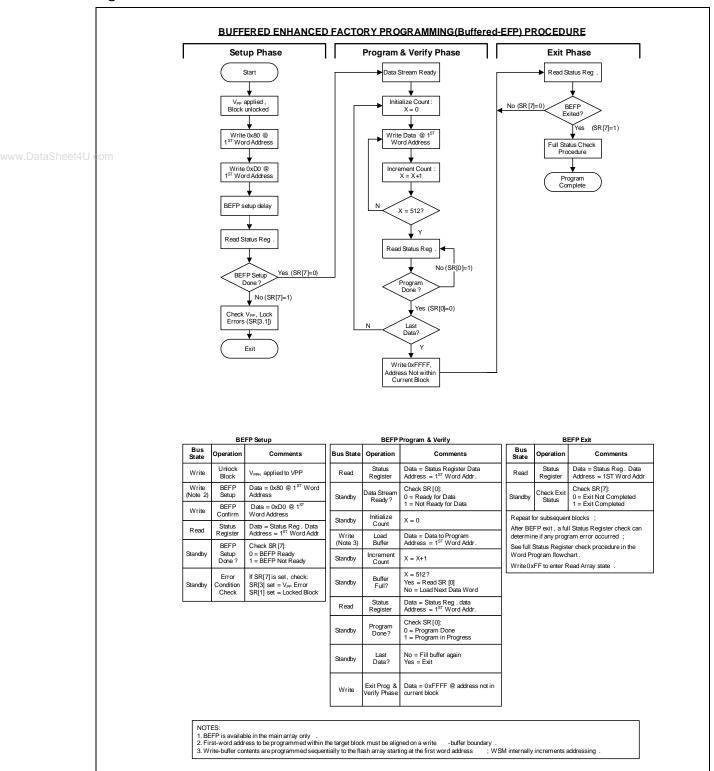

|        |            | 9.6.3 Buffered Enhanced Factory Programming (BEFP)          |     |

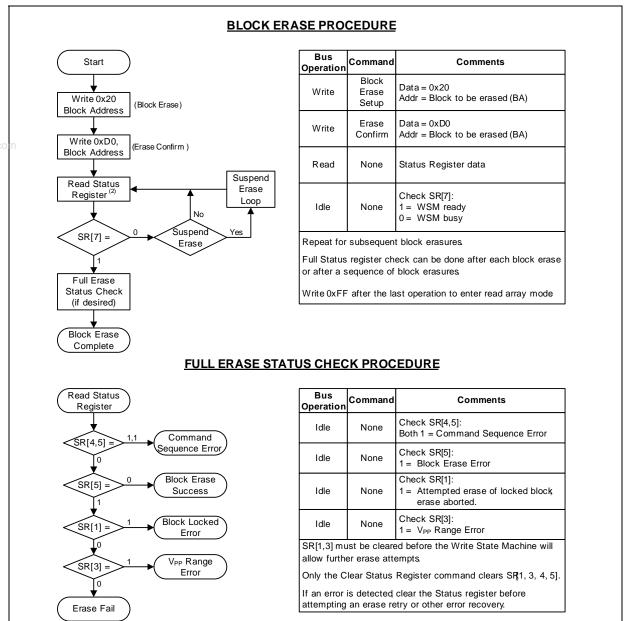

|        | 9.7        | Block Erase Operations                                      |     |

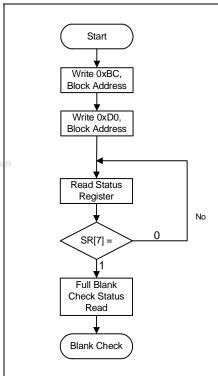

|        | 9.8        | Blank Check Operation                                       |     |

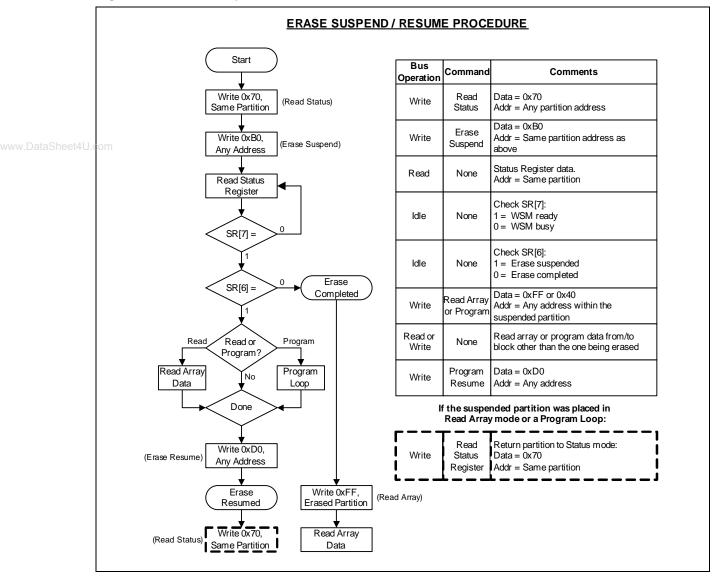

|        | 9.9        | Suspend and Resume                                          |     |

|        | 9.10       | Simultaneous Operations                                     |     |

|        |            |                                                             |     |

|        | 9.11       | Security9.11.1 Block Locking                                |     |

|        |            |                                                             |     |

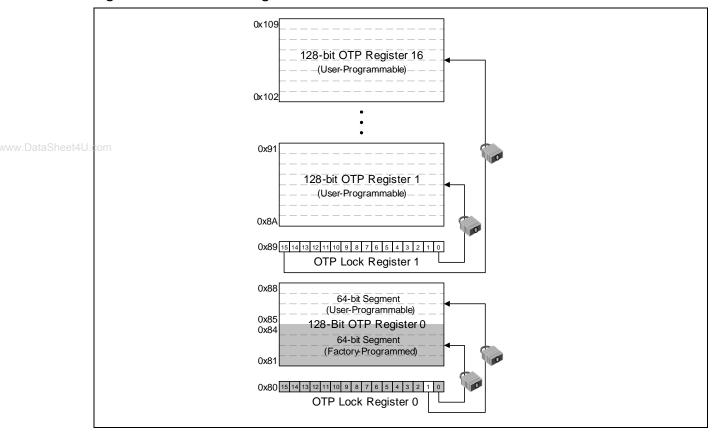

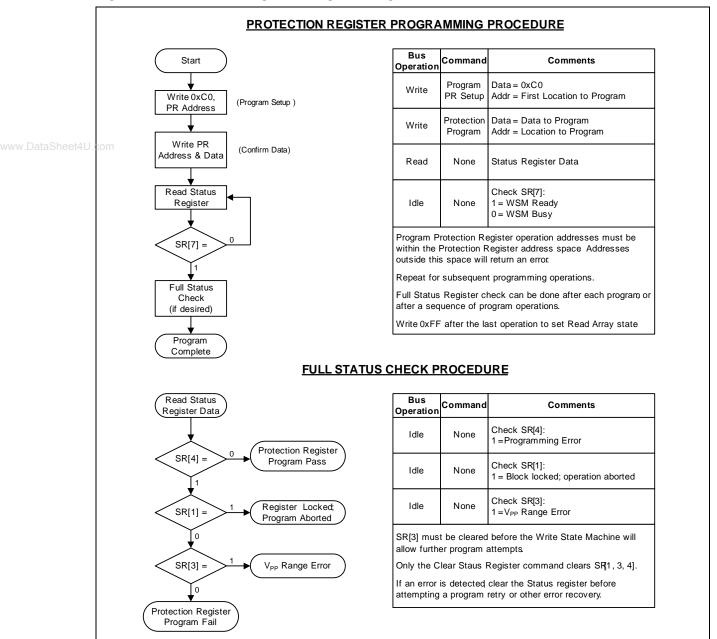

|        |            | 9.11.2 One-Time Programmable (OTP) Registers                |     |

|        |            | 9.11.3 Global Main-Array Protection                         |     |

|        |            | ce Command Codes                                            |     |

| 11.0   | Flow       | Charts                                                      | 101 |

| 12.0   | Comr       | mon Flash Interface                                         | 110 |

|        | 12.1       | Query Structure Output                                      |     |

|        | 12.2       | Block Status Register                                       |     |

|        |            |                                                             |     |

#### Numonyx™ StrataFlash® Cellular Memory (M18)

|      | 12.3 CFI Query Identification String       | 111 |

|------|--------------------------------------------|-----|

|      | 12.4 Device Geometry Definition            | 113 |

|      | 12.5 Numonyx-Specific Extended Query Table |     |

| 13.0 | Next State                                 | 20  |

| Α    | AADM Mode 1                                | 128 |

| В    | Additional Information                     | 36  |

| С    | Ordering Information                       | 136 |

/ww.DataSheet4U.com

April 2008 Order Number: 309823-11

# **Revision History**

| Date              | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|-------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 14-April-06       | 001      | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 28-April-06       | 002      | Updated the template (naming and branding). On the cover page, changed BEFP from 1.6 µs/byte (typ) to 3.2 µs/Word (typ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| com<br>20-June-06 | 003      | Correced the BEFP on the cover page to read 3.2 µs/Word and synchronized the BEFP on the cover with that in Section 7.4, "Program and Erase Characteristics" on page 68.  Added Figure 1, "Mechanical Specifications: x16D (105-ball) package (8x10x1.0 mm)" on page 14 and Figure 5, "Mechanical Specifications: x16 Split Bus (165-ball) package (10x11x1.2 mm)" on page 18.  Added the following line item part numbers:  —PF48F6000M0Y0BE  —PF38F6070M0Y0VE  —PF48F6000M0Y1BE                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| October 2006      | 004      | Removed information on the 90 nm Extended Flash Array (EFA) feature that is no longer supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| November 2006     | 005      | Revised to include 65 nm, 1-Gbit device information. Moved sections for Device ID, Additional Information, and Order Information to Functional Description chapter. Created a separate M18 Developer's Manual to include the following information:  —Bus Interface —Flash Operations —Device Command Codes —Flow Charts —Common Flash Interface —Next State Table Removed line item PF5566MMY0C0 (512+512 M18 + 128 + 128 PSRAM) and its accompanying package (8x11x1.4, x16C 107 ball).  Added the following line items: —PF48F6000M0Y0BE, 65 nm —PF38F6070M0Y0BE, 65 nm —PF38F4060M0Y0B0 —PF58F0031M0Y1BE, 65 nm —PF38F4060M0Y0C0 —PF38F4060M0Y1C0 —PF38F4060M0Y1C0 —PF38F6070M0Y0CE, 65 nm Added the following packages to support new line items: —8x10x1.0, x16D 105 ball —11x15x1.2, x16C 107 ball —8x10x1.2, x16C 107 ball —8x10x1.2, x16SB 165 ball |  |  |  |  |  |  |

| November 2006     | 006      | Updated line item information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| February 2007     | 007      | Added the following line items and package as applicable: PF48F4000M0Y0CE, 8x10x1.0 x16C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| June 2007         | 800      | Merged the Developer Manual and Datasheet content into a single document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| March 2008        | 009      | Updated the Performance specifications for 133MHz Capulet 1G improvements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| March 2007        | 800      | Updated timing diagrams in AC Characteristics section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

Datasheet April 2008 6 Order Number: 309823-11

#### Numonyx™ StrataFlash® Cellular Memory (M18)

| Date       | Revision | Description                                                                                                                                                                                  |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          | Added note stating the value of RCR8 in timing diagrams inSection 7.2.1, "Read Timing Waveforms" on page 52.                                                                                 |

| July 2007  | 009      | Resized several timing diagrams in AC Characteristics section.                                                                                                                               |

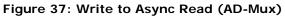

|            |          | Updated timing diagrams Figure 31, "Async Read to Write (Non-Mux)" on page 62, Figure 36, "Async Read to Write (AD-Mux)" on page 66 and Figure 37, "Write to Async Read (AD-Mux)" on page 66 |

| March 2008 | 010      | Updated Program performance specs with Capulet improved performance values.                                                                                                                  |

| April 2008 | 11       | Applied Numonyx branding.                                                                                                                                                                    |

ww.DataSheet4U.com

April 2008 Datasheet Order Number: 309823-11 7

### 1.0 Introduction

Numonyx<sup>™</sup> StrataFlash<sup>®</sup> Cellular Memory is the sixth generation Numonyx<sup>™</sup> StrataFlash<sup>®</sup> memory with multi-level cell (MLC) technology. It provides high-performance, low-power synchronous-burst read mode and asynchronous read mode at 1.8 V. It features flexible, multi-partition read-while-program and read-while-erase capability, enabling background programming or erasing in one partition simultaneously with code execution or data reads in another partition. The eight partitions allow flexibility for system designers to choose the size of the code and data segments. The Numonyx<sup>™</sup> StrataFlash<sup>®</sup> Cellular Memory is manufactured using Intel\* 65 nm ETOX\* X and 90 nm ETOX\* IX process technology and is available in industry-standard chip-scale packaging.

w.DataSheet4U.com

#### 1.1 Document Purpose

#### 1.2 Nomenclature

Table 1: Definition of Terms

| Term               | Definition                                                                                  |

|--------------------|---------------------------------------------------------------------------------------------|

| 1.8 V              | Refers to VCC and VCCQ voltage range of 1.7 V to 2.0 V                                      |

| Block              | A group of bits that erase with one erase command                                           |

| Main Array         | A group of 256-KB blocks used for storing code or data                                      |

| Partition          | A group of blocks that share common program and erase circuitry and command status register |

| Programming Region | An aligned 1-KB section within the main array                                               |

| Segment            | A 32-byte section within the programming region                                             |

| Byte               | 8 bits                                                                                      |

| Word               | 2 bytes = 16 bits                                                                           |

| Kb                 | 1024 bits                                                                                   |

| КВ                 | 1024 bytes                                                                                  |

| KW                 | 1024 words                                                                                  |

| Mb                 | 1,048,576 bits                                                                              |

| MB                 | 1,048,576 bytes                                                                             |

## 1.3 Acronyms

Table 2: List of Acronyms

| Acronym | Meaning                                 |

|---------|-----------------------------------------|

| APS     | Automatic Power Savings                 |

| CFI     | Common Flash Interface                  |

| DU      | Don't Use                               |

| ECR     | Enhanced Configuration Register (Flash) |

Table 2: List of Acronyms

| Acronym | Meaning                             |

|---------|-------------------------------------|

| ETOX    | EPROM Tunnel Oxide                  |

| FDI     | Numonyx™ Flash Data Integrator      |

| RCR     | Read Configuration Register (Flash) |

| RFU     | Reserved for Future Use             |

| SCSP    | Stacked Chip Scale Package          |

#### 1.4 Conventions

w.DataSheet4U.com

**Table 3: Datasheet Conventions**

| Convention                    | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Group Membership Brackets     | Square brackets are used to designate group membership or to define a group of signals with a similar function, such as A[21:1].                                                                                                                                                                                                                                                                                                                      |

| VCC vs. V <sub>CC</sub>       | When referring to a signal or package-connection name, the notation used is VCC. When referring to a voltage level, the notation used is subscripted such as $V_{CC}$ .                                                                                                                                                                                                                                                                               |

| Device                        | This term is used interchangeably throughout this document to denote either a particular die, or all die in the package.                                                                                                                                                                                                                                                                                                                              |

| F[3:1]-CE#,<br>F[2:1]-OE#     | This is the method used to refer to more than one chip-enable or output enable. When each is referred to individually, the reference is F1-CE# and F1-OE# (for die #1), and F2-CE# and F2-OE# (for die #2).                                                                                                                                                                                                                                           |

| F-VCC P-VCC, S-VCC            | When referencing flash memory signals, the notation used is F-VCC or F-V <sub>CC</sub> , respectively. When the reference is to PSRAM signals or timings, the notation is prefixed with "P-" (for example, P-VCC, P-V <sub>CC</sub> ).  When referencing SRAM signals or timings, the notation is prefixed with "S-" (for example, S-VCC or S-V <sub>CC</sub> ).  P-VCC and S-VCC are RFU for stacked combinations that do not include PSRAM or SRAM. |

| R-OE#, R-LB#,<br>R-UB#, R-WE# | Used to identify RAM OE#, LB#, UB#, WE# signals, and are usually shared between two or more RAM die. R-OE#, R-LB#, R-UB# and R-WE# are RFU for stacked combinations that do not include PSRAM or SRAM.                                                                                                                                                                                                                                                |

| 00FFh                         | Denotes 16-bit hexadecimal numbers                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 00FF 00FFh                    | Denotes 32-bit hexadecimal numbers                                                                                                                                                                                                                                                                                                                                                                                                                    |

## 2.0 Functional Description

#### 2.1 Product Overview

The Numonyx<sup>™</sup> StrataFlash<sup>®</sup> Cellular Memory (M18) device provides high read and write performance at low voltage on a 16-bit data bus.

The flash memory device has a multi-partition architecture with read-while-program and read-while-erase capability.

The device supports synchronous burst reads up to 108 MHz using ADV# and CLK address-latching on some litho/density combinations and up to 133 MHz using CLK address-latching only on some litho/density combinations. It is listed below in the following table.

w.DataSheet4U.com

Table 4: M18 Product Litho/Density/Frequency Combinations

| Litho (nm) | Density (Mbit) | Supports frequency up to (MHz) | Sync read address-latching |

|------------|----------------|--------------------------------|----------------------------|

| 90         | 256            | 133                            | CLK-latching               |

| 90         | 512            | 108                            | ADV#- and CLK-latching     |

|            | 128            | 133                            | CLK-latching               |

|            | 256            | 133                            | CLK-latching               |

| 65         | 512            | 133                            | CLK-latching               |

|            | 1024           | 108                            | ADV#- and CLK-latching     |

|            | 1024           | 133                            | CLK-latching               |

In continuous-burst mode, a data Read can traverse partition boundaries.

Upon initial power-up or return from reset, the device defaults to asynchronous arrayread mode. Synchronous burst-mode reads are enabled by programming the Read Configuration Register. In synchronous burst mode, output data is synchronized with a user-supplied clock signal. A WAIT signal provides easy CPU-to-flash memory synchronization.

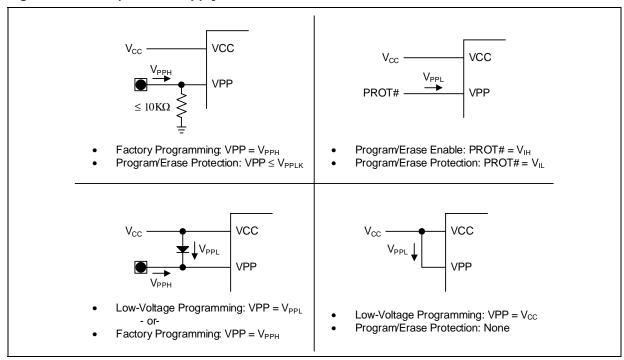

Designed for low-voltage applications, the device supports read operations with  $V_{CC}$  at 1.8 V, and erase and program operations with  $V_{PP}$  at 1.8 V or 9.0 V. VCC and VPP can be tied together for a simple, ultra-low power design. In addition to voltage flexibility, a dedicated VPP connection provides complete data protection when  $V_{PP}$  is less than  $V_{PPLK}$ .

A Status Register provides status and error conditions of erase and program operations.

One-Time-Programmable (OTP) registers allow unique flash device identification that can be used to increase flash content security. Also, the individual block-lock feature provides zero-latency block locking and unlocking to protect against unwanted program or erase of the array.

The flash memory device offers three power savings features:

- Automatic Power Savings (APS) mode: The device automatically enters APS following a read-cycle completion.

- Standby mode: Standby is initiated when the system deselects the device by deasserting CE#.

• Deep Power-Down (DPD) mode: DPD provides the lowest power consumption and is enabled by programming in the Enhanced Configuration Register. DPD is initiatied by asserting the DPD pin.

### 2.2 Configuration and Memory Map

The Numony $x^{\text{TM}}$  StrataFlash<sup>®</sup> Cellular Memory device features a symmetrical block architecture. The flash device main array is divided as follows:

- The main array of the 128-Mbit device is divided into eight 16-Mbit partitions. Each parition is divided into eight 256-KByte blocks: 8 x 8 = 64 blocks in the main array of a 128-Mbit device.

- The main array of the 256-Mbit device is divided into eight 32-Mbit partitions. Each parition is divided into sixteen 256-KByte blocks: 8 x 16 = 128 blocks in the main array of a 256-Mbit device.

- The main array of the 512-Mbit device is divided into eight 64-Mbit partitions. Each parition is divided into thirty-two 256-KByte blocks: 8 x 32 = 256 blocks in the main array of a 256-Mbit device.

- The main array of the 1-Gbit device is divided into eight 128-Mbit partitions. Each parition is divided into sixty-four 256-KByte blocks: 8 x 64 = 512 blocks in the main array of a 1-Gbit device.

Each block is divided into as many as two-hundred-fifty-six 1-KByte programming regions. Each region is divided into as many as thirty-two 32-Byte segments.

Table 5: Main Array Memory Map (Sheet 1 of 2)

|           |      |          | Mbit Device         | Mbit | 256-Mbit Device |                     |      | 512-Mbit Device |                     |      | 1-Gbit Device |                     |

|-----------|------|----------|---------------------|------|-----------------|---------------------|------|-----------------|---------------------|------|---------------|---------------------|

| Partition | Mbit | Blk<br># | Address<br>Range    |      | Blk<br>#        | Address<br>Range    | Mbit | Blk<br>#        | Address<br>Range    | Mbit | Blk<br>#      | Address<br>Range    |

|           |      | 63       | 07E0000-<br>07FFFFF |      | 127             | OFEOOOO-<br>OFFFFFF |      | 255             | 1FE0000-<br>1FFFFFF |      | 511           | 3FE0000-<br>3FFFFFF |

| 7         | 16   | :        | ÷                   | 32   | :               | ÷                   | 64   | :               | :                   | 128  |               | :                   |

|           |      | 56       | 0700000-<br>071FFFF |      | 112             | OE00000-<br>OE1FFFF |      | 224             | 1C00000-<br>1C1FFFF |      | 448           | 3800000-<br>381FFFF |

|           |      | 55       | 06E0000-<br>06FFFFF | 32   | 111             | ODE0000-<br>ODFFFFF | 64   | 223             | 1BE0000-<br>1BFFFFF | 128  | 447           | 37E0000-<br>37FFFFF |

| 6         | 16   | :        | ÷                   |      | :               | :                   |      | :               | :                   |      | :             | :                   |

|           |      | 48       | 0600000-<br>061FFFF |      | 96              | OCOOOOO-<br>OC1FFFF |      | 192             | 1800000-<br>181FFFF |      | 384           | 3000000-<br>301FFFF |

|           | 16   | 47       | 05E0000-<br>05FFFFF | 32   | 95              | OBEOOOO-<br>OBFFFFF | 64   | 191             | 17E0000-<br>17FFFFF | 128  | 383           | 2FE0000-<br>2FFFFFF |

| 5         |      | :        | i                   |      | :               | :                   |      | :               | i.                  |      | :             | :                   |

|           |      | 40       | 0500000-<br>051FFFF |      | 80              | OAOOOOO-<br>OA1FFFF |      | 160             | 1400000-<br>141FFFF |      | 320           | 2800000-<br>281FFFF |

| 4         |      | 39       | 04E0000-<br>04FFFF  |      | 79              | 09E0000-<br>09FFFFF | 64   | 159             | 13E0000-<br>13FFFFF | 128  | 319           | 27E0000-<br>27FFFF  |

|           | 16   | :        | :                   | 32   | :               | :                   |      | :               | į.                  |      | :             | i i                 |

|           |      | 32       | 0400000-<br>041FFFF |      | 64              | 0800000-<br>081FFFF |      | 128             | 1000000-<br>101FFFF |      | 256           | 2000000-<br>201FFFF |

www DataSheet4U com

Table 5: Main Array Memory Map (Sheet 2 of 2)

|      |          |      | 128-     | 8-Mbit Device       |      | 256-N    | 256-Mbit Device     |      | 512-N    | /Ibit Device        |      | 1-Gk     | oit Device          |

|------|----------|------|----------|---------------------|------|----------|---------------------|------|----------|---------------------|------|----------|---------------------|

| Pa   | artition | Mbit | Blk<br># | Address<br>Range    |

|      |          |      | 31       | 03E0000-<br>03FFFFF |      | 63       | 07E0000-<br>07FFFFF |      | 127      | OFEOOOO-<br>OFFFFFF |      | 255      | 1FE0000-<br>1FFFFFF |

|      | 3        | 16   | :        | i.                  | 32   | :        | :                   | 64   | :        | i.                  | 128  |          | i                   |

|      |          |      | 24       | 0300000-<br>031FFFF |      | 48       | 0600000-<br>061FFFF |      | 96       | OCOOOOO-<br>OC1FFFF |      | 192      | 1800000-<br>181FFFF |

| .com | 1        |      | 23       | 02E0000-<br>02FFFFF |      | 47       | 05E0000-<br>05FFFFF |      | 95       | OBEOOOO-<br>OBFFFFF |      | 191      | 17E0000-<br>17FFFFF |

|      | 2        | 16   | :        | :                   | 32   | :        | :                   | 64   | :        | :                   | 128  |          | :                   |

|      |          |      | 16       | 0200000-<br>021FFFF |      | 32       | 0400000-<br>041FFFF |      | 64       | 0800000-<br>081FFFF |      | 128      | 1000000-<br>101FFFF |

|      |          |      | 15       | 01E0000-<br>01FFFFF | 32   | 31       | 03E0000-<br>03FFFFF | 64   | 63       | 07E0000-<br>07FFFFF | 128  | 127      | OFE0000-<br>OFFFFFF |

|      | 1        | 16   | :        | :                   |      | :        | :                   |      | :        | ÷                   |      |          | :                   |

|      |          |      | 8        | 0100000-<br>011FFFF |      | 16       | 0200000-<br>021FFFF |      | 32       | 0400000-<br>041FFFF |      | 64       | 0800000-<br>081FFFF |

|      |          |      | 7        | 00E0000-<br>00FFFFF |      | 15       | 01E0000-<br>01FFFFF |      | 31       | 03E0000-<br>03FFFFF | 128  | 63       | 07E0000-<br>07FFFFF |

|      | 0        | 16   | :        | i                   | 32   | ::       | :                   | 64   |          | :                   |      |          | :                   |

|      |          |      | 0        | 0000000-<br>001FFFF |

#### 2.3 Device ID

Table 6: Device ID codes

| Density    | Litho (nm) | Product | Device I dentifier Code<br>(Hex) |

|------------|------------|---------|----------------------------------|

| 128 Mbit   | 65         | Non-Mux | 8900                             |

| 120 WDIT   | 03         | AD-Mux  | 8903                             |

| 256 Mbit   | 65, 90     | Non-Mux | 8901                             |

| 230 MDIL   | 65, 90     | AD-Mux  | 8904                             |

| 512 Mbit   | 65, 90     | Non-Mux | 887E                             |

| STZ WIDIT  | 05, 70     | AD-Mux  | 8881                             |

| 1024 Mbit  | 65         | Non-Mux | 88B0                             |

| TOZ4 WIDIT | US         | AD-Mux  | 88B1                             |

**Note:** To order parts listed above and to obtain a datasheet for the M18 SCSP parts, please contact your local Numonyx sales office.

## 3.0 Package Information

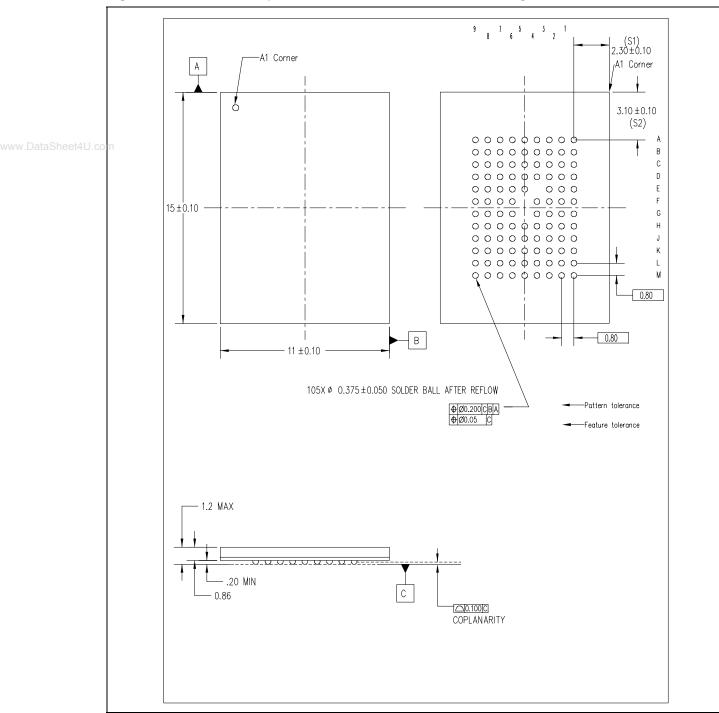

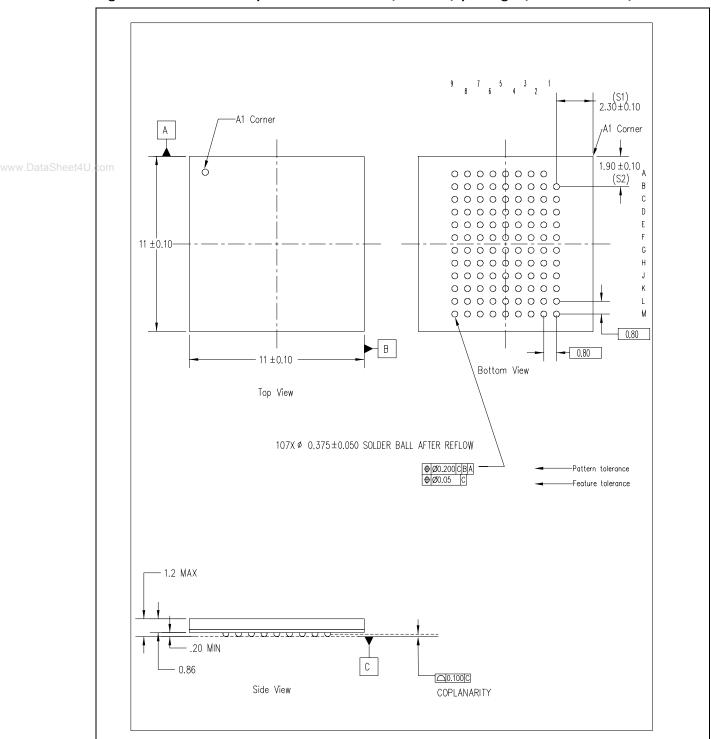

The following figures show the ballout package information for the device:

- Figure 1, "Mechanical Specifications: x16D (105-ball) package (8x10x1.0 mm)"

- Figure 2, "Mechanical Specifications: x16D (105-ball) package (8x10x1.4 mm)" on page 15

- Figure 3, "Mechanical Specifications: x16D (105-ball) package (9x11x1.2 mm)"

- Figure 4, "Mechanical Specifications: x16D (105 balls) Package (11x15x1.2 mm)" on page 17

- Figure 5, "Mechanical Specifications: x16 Split Bus (165-ball) package (10x11x1.2 mm)"

- Figure 6, "Mechanical Specifications: x16C (107-ball) package (8x10x1.0 mm)" on page 19

- Figure 7, "Mechanical Specifications: x16C (107-ball) package (8x10x1.2 mm)" on page 20

- Figure 8, "Mechanical Specifications: x16C (107-ball) package (8x11x1.2 mm)" on page 21

- Figure 9, "Mechanical Specifications: x16C (107-ball) package (11x11x1.2 mm)" on page 22

www.DataSheet4II.com

‡ S2 00000000 00000000 • 00000000 • 00000000 www.DataSheet4U.com · 000 00000 f 0000 0000 . 0000 0000 **"** 00000000 - 000000000 \* 000000000 00000000-00000000 Note: Drawing not to scale. Symbol Nom Dimensions Min Max Notes Min Nom Max 0.0394 Package Height 1.0 Α 0.200 0.0079 Ball Height **A**1 Package Body Thickness 0.0260 A2 0.660 Ball (Lead) Width 0.325 0.375 0.425 0.0128 0.0148 0.0167 b Package Body Length D 10.00 10.10 0.3898 0.3937 0.3976 Package Body Width Е 7.90 8.00 8.10 0.3110 0.3150 0.3189 Pitch 0.800 0.0315 e Ball (Lead) Count N 105 105 Y 0.100 0.0039 Seating Plane Coplanarity Corner to Ball Distance Along E S1 0.700 0.800 0.900 0.0276 0.0315 0.0354 Corner to Ball Distance Along D S2 0.500 0.600 0.700 0.0197 0.0236 0.0276

Figure 1: Mechanical Specifications: x16D (105-ball) package (8x10x1.0 mm)

S1 ‡ S2 00000000 ° 00000000 • 00000000 • 00000000 www.DataSheet4U.com · 000 00000 · 0000 0000 . 0000 0000 \* 00000000 00000000 \* 00000000-- 000000000-00000000 Note: Drawing not to scale Dimensions Symbol Min Nom Max Notes Min Nom Max 0.0551 Package Height A 1.4 0.200 0.0079 Ball Height Α1 Package Body Thickness 1.070 0.0421 A2 Ball (Lead) Width 0.325 0.375 0.425 0.0128 0.0148 0.0167 b D 9.90 10.00 10.10 0.3898 0.3937 0.3976 Package Body Length 0.3189 Package Body Width Ε 7.90 8.00 8.10 0.3110 0.3150 Pitch 0.800 0.0315 e Ball (Lead) Count N 105 105 Seating Plane Coplanarity Y 0.100 0.0039 Corner to Ball Distance Along E S10.700 0.800 0.900 0.0276 0.0315 0.0354 Corner to Ball Distance Along D S2 0.500 0.600 0.700 0.0197 0.0236 0.0276

Figure 2: Mechanical Specifications: x16D (105-ball) package (8x10x1.4 mm)

S1 Pin 1 Corner ‡ S2 00000000 00000000 · 00000000 00000000 www.DataSheet4U.com 000 00000 D 0000 0000 · 0000 0000 **" 00000000** 00000000 00000000 00000000 00000000 Е Top View - Ball Side Down Note: Drawing not to scale. Dimensions Symbol Min Min Max Nom Max Notes Nom Package Height 1.2 0.0472 A Ball Height A1 0.200 0.0079 0.0339 0.860 Package Body Thickness A2Ball (Lead) Width b 0.325 0.375 0.425 0.0128 0.0148 0.0167 Package Body Length D 10.90 11.00 0.4291 0.4331 0.4370 11.10 9.10 0.3504 0.3583 Package Body Width Ε 0.3543 Pitch 0.800 0.0315 Ball (Lead) Count N 105 105 Seating Plane Coplanarity Y 0.100 0.0039 Corner to Ball Distance Along E S11.200 1.300 1.400 0.0472 0.0512 0.0551 0.0394 0.0433 0.0472 1.000 1.100 1.200 Corner to Ball Distance Along D S2

Figure 3: Mechanical Specifications: x16D (105-ball) package (9x11x1.2 mm)

Figure 4: Mechanical Specifications: x16D (105 balls) Package (11x15x1.2 mm)

**S1** Ball one Corner S2 000000000 00000000000 000000000000 www.DataSheet4U.com 00000000000 00000000000 0000 00000 00000 00000 D 00000 00000 00000 00000 00000 00000 000000000000 00000000000 Ĵе 00000000000 000000000000 000000000 Ε Top View - Ball Side Down Note: Drawing not to scale. Millimeters Inches Dimensions Symbol Min Nom Max Notes Min Nom Max 0.0472 Package Height Α 1.2 Ball Height 0.0079 Α1 0.200 Package Body Thickness 0.860 0.0339 A2 0.0128 0.0148 Ball (Lead) Width 0.325 0.375 0.425 0.0167 b 11.00 D 10.90 11.10 0.4291 0.4331 0.4370 Package Body Length Package Body Width 10.10 Е 9.90 10.00 0.3898 0.3937 0.3976 0.650 0.0256 Pitch e Ball (Lead) Count N 165 165 Seating Plane Coplanarity Y 0.100 0.0039 Corner to Ball Distance Along E S1 1.325 1.425 1.525 0.0522 0.0561 0.0600 Corner to Ball Distance Along D 1.500 1.600 1.700 0.0591 0.0630 0.0669

Figure 5: Mechanical Specifications: x16 Split Bus (165-ball) package (10x11x1.2 mm)

S1 \$ S2 00000000 00000000 00000000 00000000 00000000 D 00000000 00000000 00000000 00000000 00000000 Ĵe 00000000 00000000 Note: Drawing not to scale. Dimensions Symbol Min Nom Max Min Nom Max Package Height A 1.0 0.0394 Ball Height A1 0.200 0.00790.660 0.0260 Package Body Thickness A2 Ball (Lead) Width 0.325 0.375 0.425 0.0128 0.0148 0.0167 b D 9.90 10.00 10.10 0.3937 0.3976 Package Body Length 0.3898 0.3189 7.90 Package Body Width Ε 8.00 8.10 0.3110 0.3150 0.800 0.0315 Pitch e 107 107 Ball (Lead) Count N Y 0.100 0.0039 Seating Plane Coplanarity S1 0.700 0.800 0.0276 0.0315 Corner to Ball Distance Along E 0.900 0.0354 Corner to Ball Distance Along D 0.500 0.600 0.700 0.0197 0.0236 0.0276

Figure 6: Mechanical Specifications: x16C (107-ball) package (8x10x1.0 mm)

S1 ‡ S2 00000000 00000000 00000000 00000000 www.DataSheet4U.com 00000000 00000000 D 00000000 00000000 00000000 00000000 00000000 00000000 Note: Drawing not to scale Dimensions Symbol Min Nom Max Notes Min Nom Max Package Height 0.0472 A 1.2 0.200 0.0079 Ball Height A1 Package Body Thickness 0.860 0.0339 A2 Ball (Lead) Width 0.0148 0.325 0.375 0.425 0.0128 0.0167 b Package Body Length D 9.90 10.00 10.10 0.3898 0.3937 0.3976 Package Body Width Е 7.90 8.00 8.10 0.3110 0.3150 0.3189 0.800 0.0315 Pitch e Ball (Lead) Count N 107 107 Seating Plane Coplanarity Y 0.100 0.0039 Corner to Ball Distance Along E S10.700 0.800 0.900 0.0276 0.0315 0.0354 Corner to Ball Distance Along D S2 0.500 0.600 0.700 0.0197 0.0236 0.0276

Figure 7: Mechanical Specifications: x16C (107-ball) package (8x10x1.2 mm)

Pin 1 S1 Corner ‡ S2 0000000 00000000 00000000 00000000 00000000 D 00000000 00000000 00000000 00000000 00000000 00000000 00000000 Ε Top View - Ball Side Down Note: Drawing not to scale Millimeters Inches Notes Symbol Min Nom Max Max Dimensions Min Nom 1.2 0.0472 Package Height Ball Height A1 0.200 0.0079 Package Body Thickness A2 0.860 0.0339 0.325 0.375 0.425 0.0128 0.0148 Ball (Lead) Width b 0.0167 D 10.90 11.00 11.10 0.4291 0.4331 0.4370 Package Body Length 7.90 8.00 8.10 0.3110 0.3150 0.3189 Package Body Width Е 0.800 0.0315 Pitch e Ball (Lead) Count N 107 107 Seating Plane Coplanarity Y 0.100 0.0039 Corner to Ball Distance Along E S1 0.700 0.800 0.900 0.0276 0.0315 0.0354 Corner to Ball Distance Along D S2 1.000 1.100 1.200 0.0394 0.0433 0.0472

Figure 8: Mechanical Specifications: x16C (107-ball) package (8x11x1.2 mm)

Figure 9: Mechanical Specifications: x16C (107-ball) package (11x11x1.2 mm)

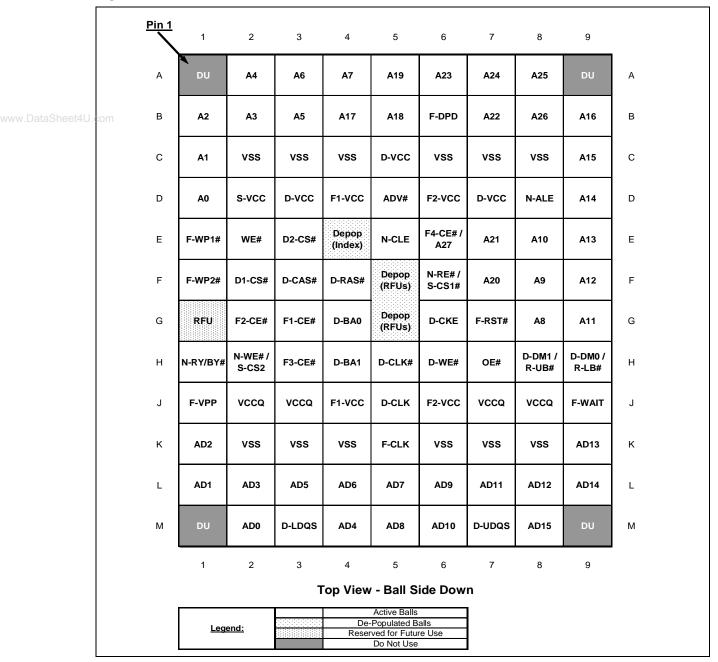

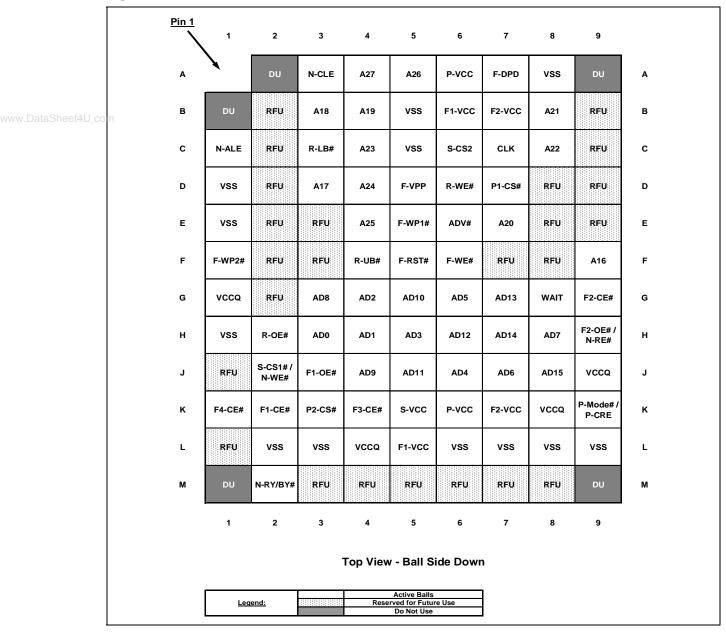

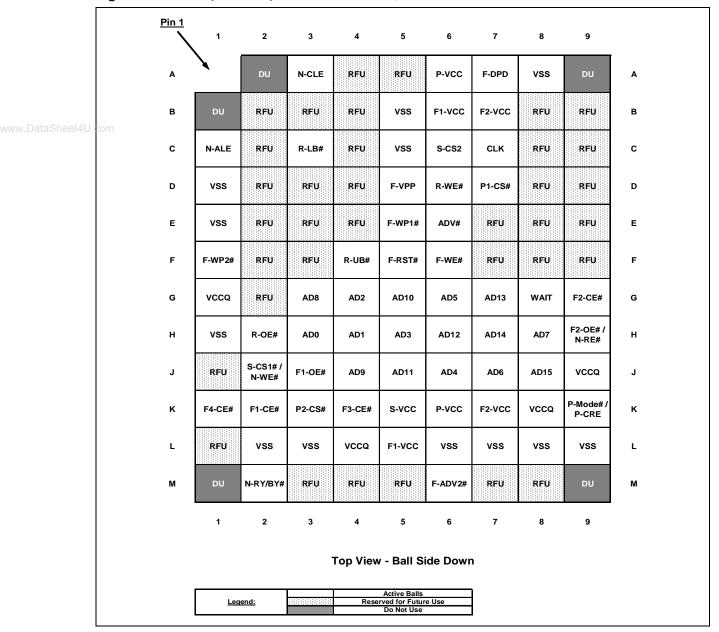

## 4.0 Ballouts and Signal Descriptions

This section provides ballout and signal description information for x16D (105-ball), x16C (107-ball), and x16 Split Bus (165-ball) packages, Non-Mux, AD-Mux, AA/D Mux interfaces.

## 4.1 Ballouts, x16D

### 4.1.1 x16D (105-Ball) Ballout, Non-Mux

Figure 10: x16D (105-Ball) Electrical Ballout, Non-Mux

| - igure re |                                 | <b>\</b>   |                  |                                                   |                  |                 |                   | -      |                  |                  |   |

|------------|---------------------------------|------------|------------------|---------------------------------------------------|------------------|-----------------|-------------------|--------|------------------|------------------|---|

|            | Pin 1                           | 1          | 2                | 3                                                 | 4                | 5               | 6                 | 7      | 8                | 9                |   |

|            | Α                               | DU         | A4               | A6                                                | A7               | A19             | A23               | A24    | A25              | DU               | А |

|            | В                               | A2         | А3               | A5                                                | A17              | A18             | F-DPD             | A22    | A26              | A16              | В |

|            | С                               | <b>A</b> 1 | vss              | vss                                               | vss              | D-VCC           | vss               | vss    | vss              | A15              | С |

|            | D                               | A0         | s-vcc            | D-VCC                                             | F1-VCC           | ADV#            | F2-VCC            | D-VCC  | N-ALE            | A14              | D |

|            | E                               | F-WP1#     | WE#              | D2-CS#                                            | Depop<br>(Index) | N-CLE           | F4-CE# /<br>A27   | A21    | A10              | A13              | Е |

|            | F                               | F-WP2#     | D1-CS#           | D-CAS#                                            | D-RAS#           | Depop<br>(RFUs) | N-RE# /<br>S-CS1# | A20    | А9               | A12              | F |

|            | G                               | RFU        | F2-CE#           | F1-CE#                                            | D-BA0            | Depop<br>(RFUs) | D-CKE             | F-RST# | A8               | A11              | G |

|            | н                               | N-RY/BY#   | N-WE# /<br>S-CS2 | F3-CE#                                            | D-BA1            | D-CLK#          | D-WE#             | OE#    | D-DM1 /<br>S-UB# | D-DM0 /<br>S-LB# | н |

|            | J                               | F-VPP      | VCCQ             | VCCQ                                              | F1-VCC           | D-CLK           | F2-VCC            | VCCQ   | VCCQ             | F-WAIT           | J |

|            | К                               | DQ2        | vss              | vss                                               | vss              | F-CLK           | vss               | vss    | vss              | DQ13             | К |

|            | L                               | DQ1        | DQ3              | DQ5                                               | DQ6              | DQ7             | DQ9               | DQ11   | DQ12             | DQ14             | L |

|            | М                               | DU         | DQ0              | D-LDQS                                            | DQ4              | DQ8             | DQ10              | D-UDQS | DQ15             | DU               | М |

|            |                                 | 1          | 2                | 3                                                 | 4                | 5               | 6                 | 7      | 8                | 9                |   |

|            |                                 |            |                  | 1                                                 | op View          | - Ball S        | ide Dow           | n      |                  |                  |   |

|            | Legend: De-Popular Reserved for |            |                  | Active Balls Populated B rved for Futu Do Not Use | re Use           |                 |                   |        |                  |                  |   |

|            |                                 |            |                  |                                                   |                  |                 |                   | -      |                  |                  |   |

#### 4.1.2 x16D (105-Ball) Ballout, AD-Mux

Figure 11: x16D (105-Ball) Electrical Ballout, AD-Mux

## 4.1.3 x16D Mux (105-Ball) Ballout, AA/D Mux

Figure 12: x16D (105-Ball) Electrical Ballout, AA/D Mux

|    | Pin 1                     | 1          | 2                | 3                                       | 4                                     | 5              | 6                | 7      | 8                | 9                |   |

|----|---------------------------|------------|------------------|-----------------------------------------|---------------------------------------|----------------|------------------|--------|------------------|------------------|---|

|    | A                         | DU         | A4               | A6                                      | A7                                    | RFU            | RFU              | RFU    | RFU              | DU               | A |

| om | В                         | A2         | А3               | A5                                      | RFU                                   | RFU            | F-DPD            | RFU    | F-ADV2#          | RFU              | В |

|    | С                         | <b>A</b> 1 | vss              | vss                                     | vss                                   | D-VCC          | vss              | vss    | vss              | A15              | С |

|    | D                         | Α0         | s-vcc            | D-VCC                                   | F-VCC                                 | F-ADV#         | F-VCC            | D-VCC  | N-ALE            | A14              | D |

|    | E                         | F-WP1#     | WE#              | D2-CS#                                  | Depop<br>(Index)                      | N-CLE          | F4-CE#           | RFU    | A10              | A13              | E |

|    | F                         | F-WP2#     | D1-CS#           | D-CAS#                                  | D-RAS#                                | Depop<br>(RFU) | S-CS1 /<br>N-RE# | RFU    | А9               | A12              | F |

|    | G                         | RFU        | F2-CE#           | F1-CE#                                  | D-BA0                                 | Depop<br>(RFU) | D-CKE            | F-RST# | A8               | A11              | G |

|    | Н                         | N-RY/BY#   | S-CS2 /<br>N-WE# | F3-CE#                                  | D-BA1                                 | D-CLK#         | D-WE#            | OE#    | D-DM1 /<br>S-UB# | D-DM0 /<br>S-LB# | н |

|    | J                         | F-VPP      | VCCQ             | VCCQ                                    | F-VCC                                 | D-CLK          | F-VCC            | VCCQ   | VCCQ             | F-WAIT           | J |

|    | к                         | AD2        | vss              | vss                                     | vss                                   | F-CLK          | vss              | vss    | vss              | AD13             | к |

|    | L                         | AD1        | AD3              | AD5                                     | AD6                                   | AD7            | AD9              | AD11   | AD12             | AD14             | L |

|    | М                         | DU         | AD0              | D-LDQS                                  | AD4                                   | AD8            | AD10             | D-UDQS | AD15             | DU               | М |

|    | ·                         | 1          | 2                | 3                                       | 4                                     | 5              | 6                | 7      | 8                | 9                |   |

|    | Top View - Ball Side Down |            |                  |                                         |                                       |                |                  |        |                  |                  |   |

|    |                           |            |                  |                                         |                                       | Active Balls   |                  | Ī      |                  |                  |   |

|    |                           | Lege       | end:             |                                         | De-Populated Balls                    |                |                  |        |                  |                  |   |

|    |                           |            |                  | 0 4 1 4 1 4 1 4 1 4 1 4 1 4 1 4 1 4 1 4 | Reserved for Future Use<br>Do Not Use |                |                  |        |                  |                  |   |

|    |                           |            |                  |                                         |                                       |                |                  |        |                  |                  |   |

ww.DataSheet4U.co

# 4.2 Signal Descriptions, x16D

Table 7: Signal Descriptions, x16D Non-Mux/AD-Mux; x16D AA/D-Mux (Sheet 1 of 4)

| Symbol           | Туре              | Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Notes |

|------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Address an       | d Data S          | ignals, Non-Mux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| com<br>A[MAX: 0] | Input             | ADDRESS: Global device signals.  Shared address inputs for all memory die during Read and Write operations.  4 -Gbit: AMAX = A27  2 -Gbit: AMAX = A26  1 -Gbit: AMAX = A25  512-Mbit: AMAX = A24  256-Mbit: AMAX = A23  128-Mbit: AMAX = A22  A[12:0] are the row and A[9:0] are the column addresses for 512-Mbit LPSDRAM.  A[12:0] are the row and A[8:0] are the column addresses for 256-Mbit LPSDRAM.  A[11:0] are the row and A[8:0] are the column addresses for 128-Mbit LPSDRAM.  Unused address inputs should be treated as RFU.                                                                                                                                                                   | 1     |

| DQ[15:0]         | Input/<br>Output  | DATA INPUT/OUTPUTS: Global device signals.  DQ[15:0] are used to input commands and write-data during Write cycles, and to output readdata during Read cycles. During NAND accesses, DQ[7:0] are used to input commands, addressdata, and write-data, and to output read-data.  Data signals are High-Z when the device is deselected or its output is disabled.                                                                                                                                                                                                                                                                                                                                             |       |

| F-ADV#           | Input             | FLASH ADDRESS VALID: Flash-specific signal; low-true input.  During synchronous flash Read operations, the address is latched on the rising edge of F-ADV#, or on the first rising edge of F-CLK after F-ADV# goes low for devices that support up to 108 MHz, or on the last rising edge of F-CLK after F-ADV# goes low for devices that support up to 133 MHz.  In an asynchronous flash Read operation, the address is latched on the rising edge of F-ADV# or continuously flows through while F-ADV# is low.                                                                                                                                                                                            |       |

| Address an       | d Data S          | ignals, AD-Mux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| A[MAX:16]        | Input             | ADDRESS: Global device signals.  Shared address inputs for all Flash and SRAM memory die during Read and Write operations.  • 4-Gbit: AMAX = A27  • 2-Gbit: AMAX = A26  • 1-Gbit: AMAX = A25  • 512-Mbit: AMAX = A24  • 256-Mbit: AMAX = A23  • 128-Mbit: AMAX = A22  Unused address inputs should be treated as RFU.                                                                                                                                                                                                                                                                                                                                                                                        | 1     |

| AD[15:0]         | Input /<br>Output | ADDRESS-DATA MULTIPLEXED INPUTS/ OUTPUTS: AD-Mux flash and SRAM lower address and data signals; LPSDRAM data signals.  During AD-Mux flash and SRAM Write cycles, AD[15:0] are used to input the lower address followed by commands or write-data.  During AD-Mux flash Read cycles, AD[15:0] are used to input the lower address followed by read-data output.  During LPSDRAM accesses, AD[15:0] are used to input commands and write-data during Write cycles or to output read-data during Read cycles.  During NAND accesses, AD[7:0] are used to input commands, address, or write-data, and to output read-data.  AD[15:0] are High-Z when the flash or SRAM is deselected or its output is disabled. |       |

| A[15:0]          | Input             | RFU, except for DRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

ww.DataSheet4

Table 7: Signal Descriptions, x16D Non-Mux/AD-Mux; x16D AA/D-Mux (Sheet 2 of 4)

| Symbol            | Туре              | Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Notes |

|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| F-ADV#            | Input             | FLASH ADDRESS VALID: Flash-specific signal; low-true input.  During synchronous flash Read operations, the address is latched on the rising edge of F-ADV#, or on the first rising edge of F-CLK after F-ADV# goes low for devices that support up to 108 MHz, or on the last rising edge of F-CLK after F-ADV# goes low for devices that support up to 133 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|                   |                   | In an asynchronous flash Read operation, the address is latched on the rising edge of F-ADV#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| a[MAX: 0]         | Input             | ADDRESS: Global device signals.  Shared address inputs for all memory die during Read and Write operations.  4-Gbit: AMAX = A27  2-Gbit: AMAX = A26  1-Gbit: AMAX = A25  512-Mbit: AMAX = A24  256-Mbit: AMAX = A23  128-Mbit: AMAX = A22  A[12:0] are the row and A[9:0] are the column addresses for 512-Mbit LPSDRAM.  A[12:0] are the row and A[8:0] are the column addresses for 256-Mbit LPSDRAM.  A[11:0] are the row and A[8:0] are the column addresses for 128-Mbit LPSDRAM.  Unused address inputs should be treated as RFU.                                                                                                                                                                                                                                                                                                                       | 1     |

| AD[15:0]          | Input /<br>Output | ADDRESS-DATA MULTIPLEXED INPUTS/ OUTPUTS: AAD-Mux flash address and data; LPSDRAM data.  During AAD-Mux flash Write cycles, AD[15:0] are used to input the upper address, lower address, and commands or write-data.  During AAD-Mux flash Read cycles, AD[15:0] are used to input the upper address and lower address, and output read-data.  During LPSDRAM accesses, AD[15:0] are used to input commands and write-data during Write cycles or to output read-data during Read cycles.  During NAND accesses, AD[7:0] are used to input commands, address-data, or write-data, and to output read-data.  AD[15:0] are High-Z when the device is deselected or its output is disabled.                                                                                                                                                                      |       |

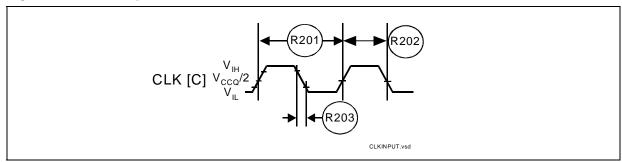

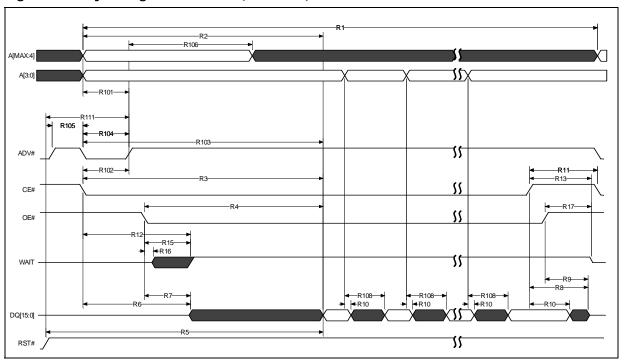

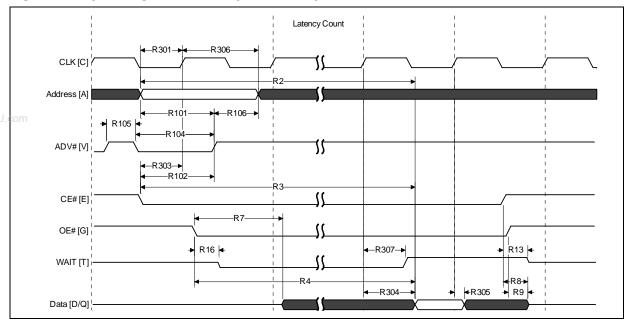

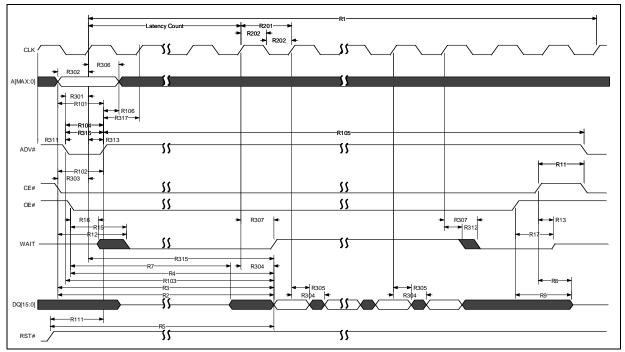

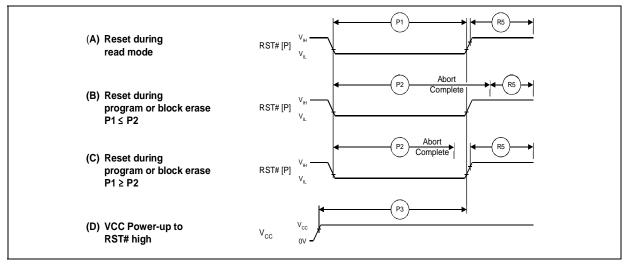

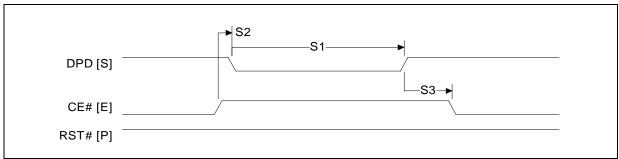

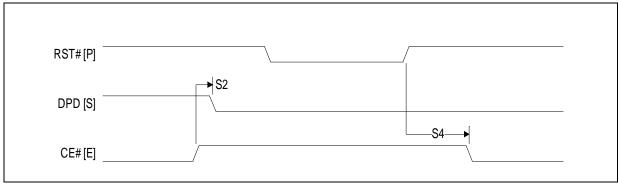

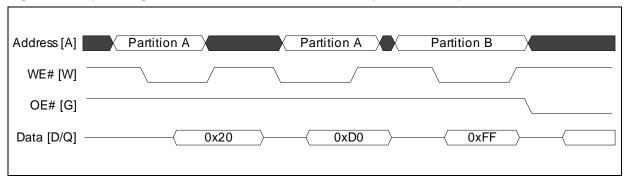

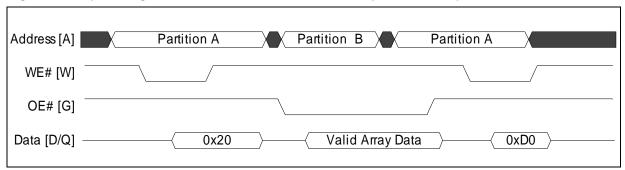

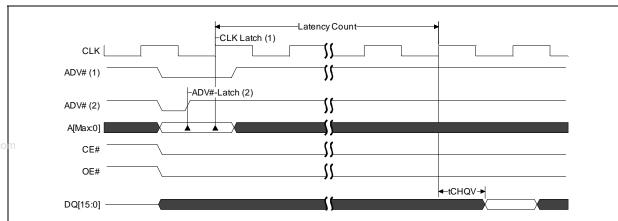

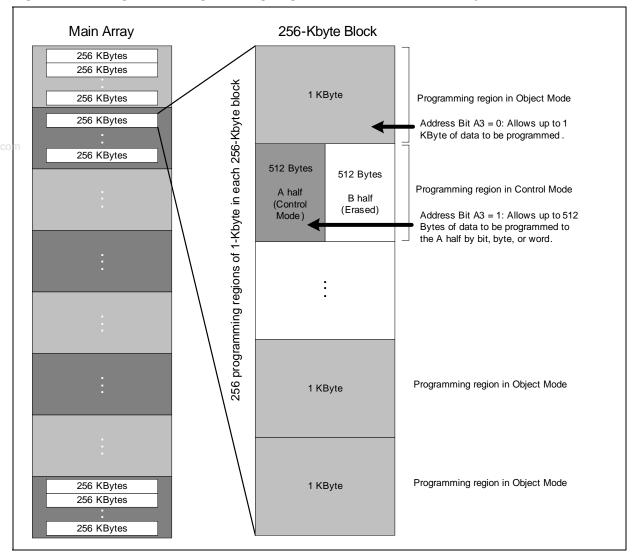

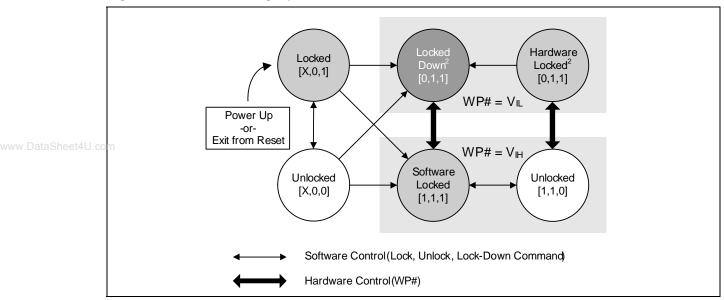

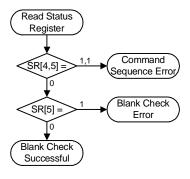

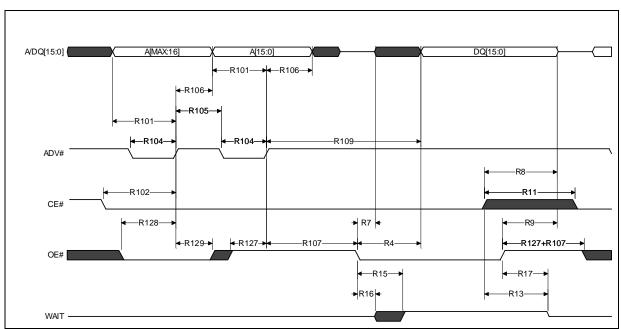

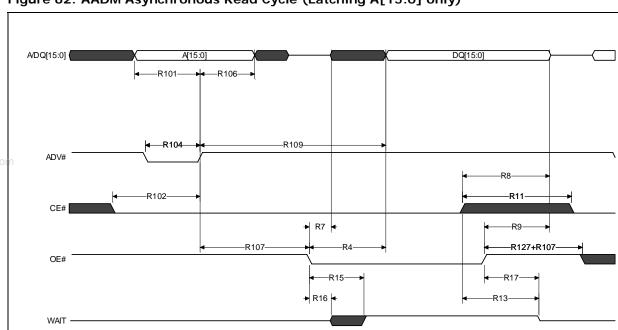

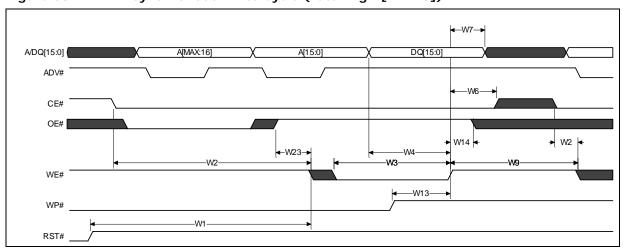

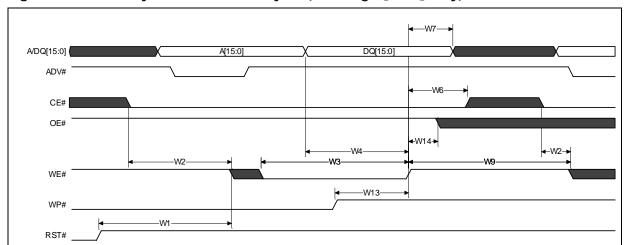

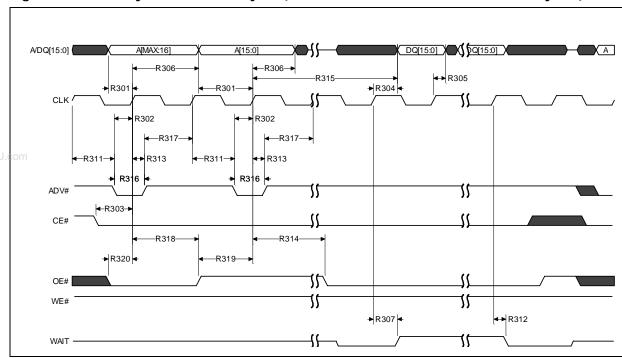

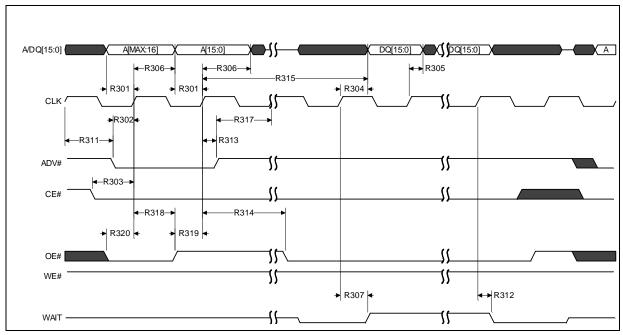

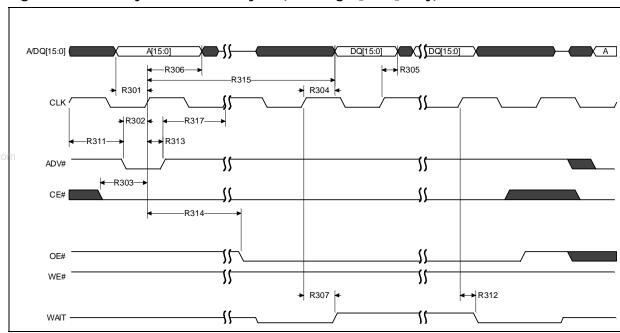

| F-ADV#<br>F-ADV2# | Input             | FLASH ADDRESS VALID: Flash-specific signal; low-true input.  During a synchronous flash Read operation, the address is latched on the F-ADV# rising edge or the first F-CLK edge after F-ADV# low in devices that support up to 104 MHz, and on the last rising F-CLK edge after F-ADV# low in devices that support upto 133 MHz.  During a synchronous flash Read operation, the address is latched on the rising edge of F-ADV# or the first active F-CLK edge whichever occurs first.  In an asynchronous flash Read operation, the address is latched on the rising edge of F-ADV#.  During AAD-Mux flash accesses, the upper address is latched on the valid edge of F-CLK while F-ADV2# is low; the lower address is latched on the valid edge of F-CLK while F-ADV# is low.  The upper address is always latched first, followed by the lower address. |       |